Heterogeneous Integration and 2.5D/3D IC Packaging Market Size, Share & Trends Analysis Report by Technology Type (2.5D IC Packaging, 3D IC Packaging, Chiplet-based Integration, Hybrid Bonding), Interconnect Technology, Packaging Platform, Chip Configuration, Wafer Size, Node Technology, Material Type, End-Use Industry, and Geography (North America, Europe, Asia Pacific, Middle East, Africa, and South America) – Global Industry Data, Trends, and Forecasts, 2026–2035

|

|

|

Segmental Data Insights |

|

|

Demand Trends |

|

|

Competitive Landscape |

|

|

Strategic Development |

|

|

Future Outlook & Opportunities |

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market Size, Share, and Growth

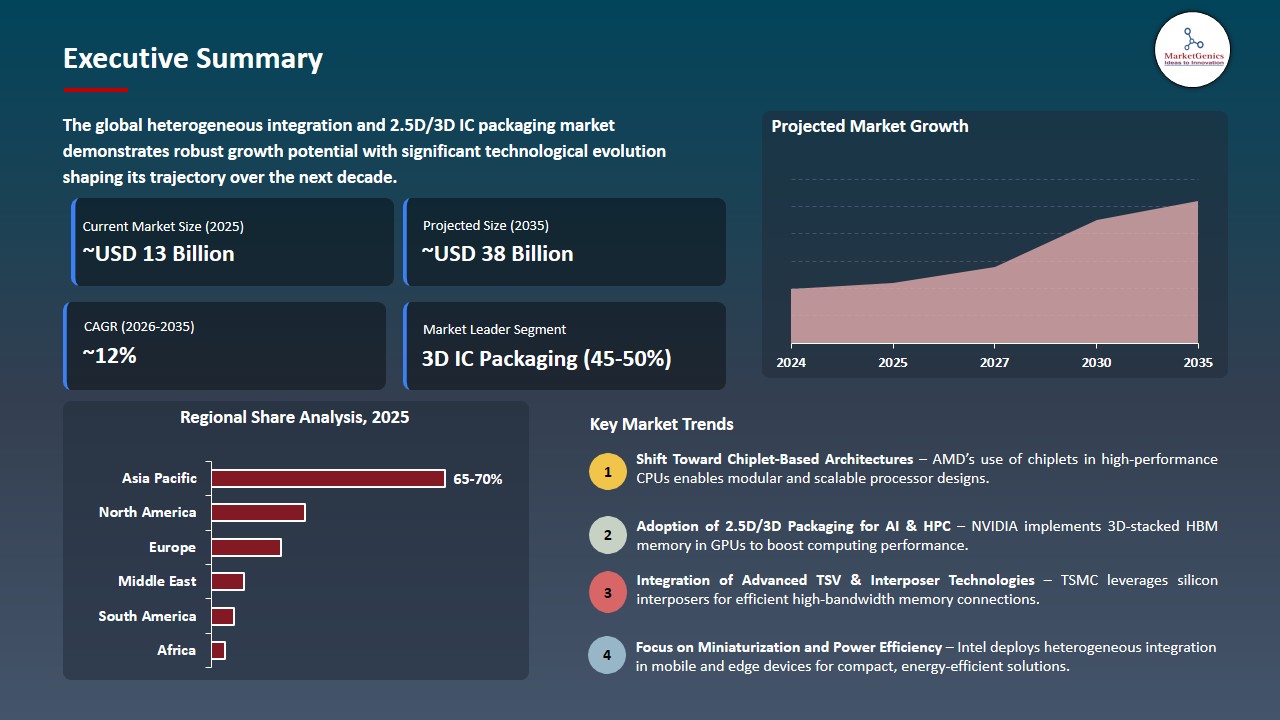

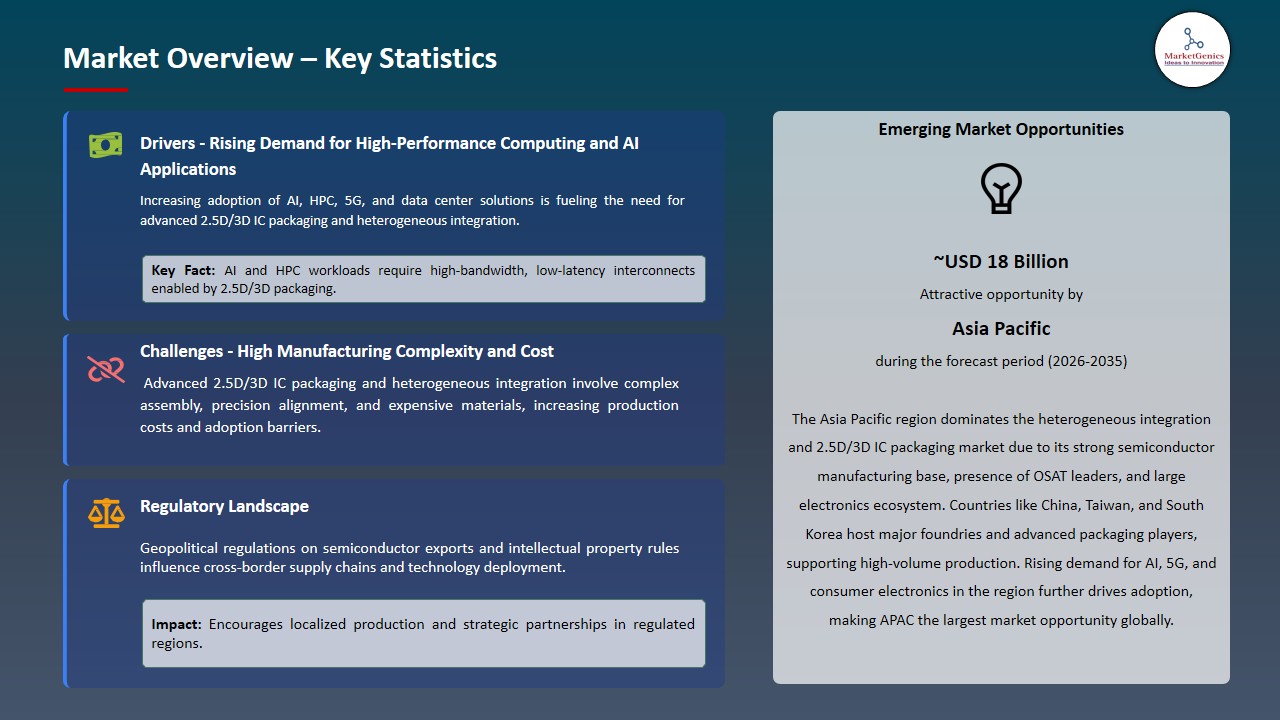

The global heterogeneous integration and 2.5D/3D IC packaging market is experiencing robust growth, with its estimated value of USD 12.7 billion in the year 2025 and USD 38.4 billion by 2035, registering a CAGR of 11.7%, during the forecast period. The demand for heterogeneous integration and 2.5D/3D IC packaging is driven by the need for higher performance, miniaturization, and energy-efficient solutions in AI, HPC, 5G, and automotive electronics, alongside growing adoption of advanced chiplet-based architectures and rising semiconductor manufacturing capabilities in Asia Pacific.

Soitec’s CTO and senior EVP Innovation, Christophe Maleville said: “Our collaboration with PSMC reflects a shared commitment to pushing the boundaries of 3D integration and supporting the global shift toward more efficient and compact computing architectures. Together we are laying the groundwork for the next generation of semiconductor innovation.”

The growing popularity of AI training, inference, and high-performance computing workloads is driving the demand of heterogeneous integration and 2.5D/3D IC packaging market because advanced packaging allows tight integration of logic and high-bandwidth memory, and has a greater density of interconnect and power efficiency that can no longer be achieved by monolithic scaling. For instance, in 2025, as advanced packaging like TSMC’s CoWoS 2.5D/SoIC 3D platforms are adopted by major AI GPU customers to deliver ultra-high bandwidth and performance. This driver is accelerating market growth by making advanced 2.5D/3D packaging essential for scaling AI and HPC performance while controlling power consumption and system complexity.

Additionally, the increasing demand in 2.5D/3D IC packaging due to the increasing requirements in chiplet-based and heterogeneous system integration, as the configuration can be designed in a more modular way, the time-to-market is reduced, and yield is better than monolithic SoCs. For instance, in 2025, Intel has expanded its Foveros Direct 3D and EMIB platforms to enable high-density chiplet integration of AI and data center processors. This driver is increasing market adoption by making available to scalability, cost, performance-optimized semiconductor layouts in end-use sectors.

Key adjacent market opportunities for heterogeneous integration and 2.5D/3D IC packaging include AI and HPC accelerators, high-bandwidth memory (HBM), advanced substrates and interposers, chiplet-based automotive electronics, and silicon photonics integration for data centers and networking. The presence of these adjacencies is highly expansive in terms of the market size to be addressed and provides long-term growth.

Heterogeneous Integration and 2.5D/3D IC Packaging Market Dynamics and Trends

Driver: Increasing Demand for Energy-Efficient High-Performance Computing Solutions

-

The significant exponential increase in AI, machine learning, and high-performance computing (HPC) workloads has changed the priorities of semiconductor design to the architectures that provide greater computational density and better power efficiency. Monolithic scaling has encountered physical and economic constraints and it is now necessary to adopt heterogeneous integration and 2.5D/3D IC packaging as the future computing applications require.

- These superior packaging technologies allow a close co-location of logic dies with high-bandwidth memory (HBM), and other specialized accelerators in small, thermally-specialized designs, with a tremendous increase in performance-per-watt. In 2025, Intel announced its Foveros Direct 3D packaging, which vertically stacked chiplets with sub-10 -hybrid bonding, which increased the data throughput with reduced power loss compared to the previous techniques.

- This trend is increasing the use of advanced packaging as a fundamental enabler to high-performance computing by making scalable modular designs optimize the performance and energy usage.

- It is increasing market development through making energy-efficient and high-performance semiconductor solutions ever more vital in data centers, AI, and HPC ecosystems.

Restraint: Thermal Management and Reliability Challenges in High-Density Packages

-

The critical thermal management issues arise in heterogeneous integration and 2.5D/3D IC packaging market due to increased densities of dies and vertical stacking. Multi-die architectures with high-power densities create hotspots that may cause a decrease in performance, lifespan, and signal integrity and mechanical reliability, and raise the complexity of design and manufacturing.

- For instance, companies like ASE Technology encountered engineering hurdles while implementing high-density packaging for AI accelerators and HPC processors. Addressing these issues required advanced heat spreaders, improved thermal interface materials, and careful design optimization to prevent overheating and ensure long-term reliability.

- These issues add complexity, cost and design cycle-time to production and it is hard to scale solutions quickly by the manufacturer.

- Thermal and reliability limits can decelerate the use of advanced and 2.5D/3D packaging and inhibit market development as demand for high-performance computing products which are energy efficient continues to increase.

Opportunity: Expansion of 5.5D and Multi-Die Integration Technologies

-

The heterogeneous integration and 2.5D/3D IC packaging market is experiencing significant opportunities by creating 5.5D and multi-die integration platforms. These technologies permit the realization of the integration of a variety of heterogeneous dies, such as logic, memory, and specialized accelerators, into a single package, with greater interconnect density, reduced latency and better power efficiency than the conventional 2.5D and 3D designs.

- For instance, Socionext’s expanded 3DIC and 5.5D packaging portfolio, utilizing TSMC’s SoIC-X face-to-face stacking, demonstrates the ability to deliver compact, high-performance systems optimized for AI, machine learning, and consumer electronics applications. These platforms facilitate simpler design complexity, enhanced thermal management as well as accelerating time to market of next-generation semiconductor products with the ability to create modular and scalable architectures.

- The developments also present new growth opportunities by enabling energy-saving, high performance and compact computing solutions.

- This market opportunity creates growth in adjacent markets, specifically AI accelerators and advanced consumer device designs, which will expand the use of heterogeneous integration and multi-die packages across the world.

Key Trend: Shift Toward Electrification and Polymer‑Intensive Electric Vehicles

-

The hybrid bonding and dense interconnect technologies in heterogeneous integration, and 2.5D / 3D IC packaging market are producing higher performance and scalable chiplet architecture. Sub-10um hybrid stacking allows vertical die integration which enhances signal integrity, lowers power loss, and high bandwidth communication between logic and memory and accelerators.

- Leading manufacturers, such as Intel with its Foveros Direct 3D technology and TSMC with its SoIC face-to-face stacked chiplets in 2024–2025, are commercializing these solutions to meet the growing performance demands of AI, HPC, and networking applications. By replacing traditional through-silicon vias (TSVs), thus enabling smaller packages, thermal performance, as well as more efficient utilization of silicon space.

- Additionally, this trend promotes the creation of modular and high-density semiconductor structures, which makes the devices smaller and consume less energy.

- Hybrid bonding and dense interconnect adoption enhance performance, reduce form factors, and drive the shift toward scalable, high-bandwidth, and energy-efficient computing systems.

Heterogeneous-Integration-and-2.5D/3D-IC-Packaging-Market Analysis and Segmental Data

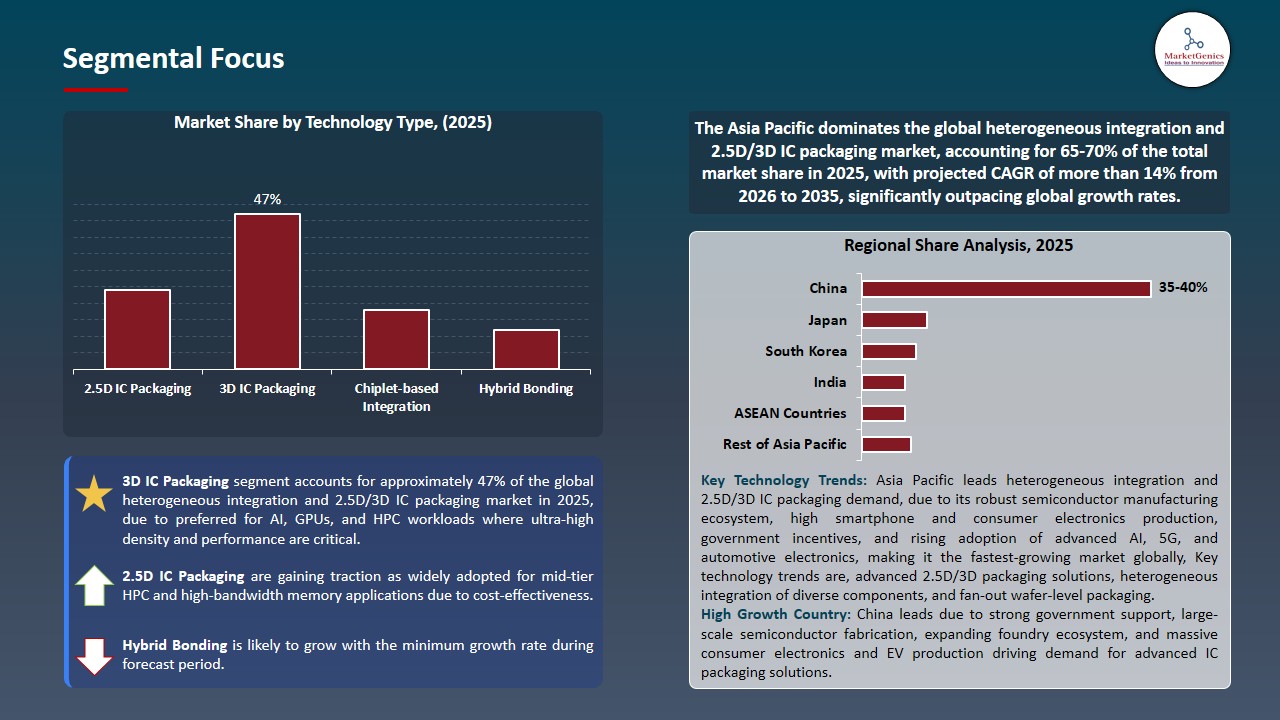

3D IC Packaging Dominate Global Heterogeneous Integration and 2.5D/3D IC Packaging Market

-

The 3D IC packaging segment dominates the global heterogeneous integration and 2.5D/3D IC packaging market, since 3D IC packaging has become a strong technology with a significant market share by virtue of its high vertical integration potential. It also facilitates high-density interconnect, minimize signal latency and has a better power efficiency than the conventional planar packaging solutions.

- The 3D ICs allow closer proximity of logic, memory and accelerators by placing more than one die within a single package. These a layout is essential to support the increased performance and power needs of AI, high-performance computing (HPC) and high-performance networking systems, in which traditional 2D layouts are becoming a bottleneck.

- For example, leading foundries and OSATs such as TSMC and Samsung have scaled 3D stacking solutions like SoIC and vertical HBM integration in 2024–2025 to support next-generation GPUs and data center processors. These implementations highlight strong industry adoption and confidence in 3D IC technologies for high-performance applications.

- The prevalence of 3D IC packaging expands the growth of the market as it enables small, energy-saving, high-performance semiconductor modules to be applied in artificial intelligence, high-performance computers and networking.

Asia Pacific Leads Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Demand

-

Asia Pacific leads the heterogeneous integration and 2.5D/3D IC packaging market, owing to which is receiving large volume demand on heterogeneous integration and 2.5D/3D IC solutions. There are large foundries, OSATs, and IDM plants operating in countries like China, Taiwan, South Korea and Japan to manufacture high performance chips that run consumer electronics, automotive and AI applications.

- For instance, in August 2025, TSMC’s advanced 2.5D/3D packaging capacity in Taiwan such as CoWoS and SoIC production has been expanding rapidly, with monthly throughput projected to double by 2025 to meet strong orders from major AI GPU and HPC customers, reflecting the region’s dominant role in advanced packaging production and demand.

- Additionally, robust government backing and industrial policy projects within the area, which enhances investment in research and development, infrastructure growth, and domestic manufacturing. The domestic and export-based IC packaging has been fueled by China semiconductor strategies and Japan subsidized advanced packaging expansions. This cohesive policy climate adds to the competitive advantages of the Asia Pacific and expediency in the use of progressive heterogeneous integration technologies.

- These factors establish Asia Pacific as the global leader in 2.5D/3D IC packaging, driving demand, accelerating adoption, and reinforcing dominance in advanced semiconductor manufacturing and high-performance computing.

Heterogeneous-Integration-and-2.5D/3D-IC-Packaging-Market Ecosystem

The global heterogeneous integration and 2.5D/3D IC packaging market is highly consolidated, with high concentration among key players such as Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics Co., Ltd., Intel Corporation, ASE Technology Holding Co., Ltd., and Amkor Technology, dominates through high degrees of concentration due to their developed packaging capabilities, strategic allies with them and their high volume manufacturing capacity which makes them lead in the high-performance computing field, artificial intelligence (AI) and the consumer electronics industry.

The consolidation of the market leaders facilitates innovation, high-quality advanced packaging solutions and competitive barriers that lead to the sustained growth and technological leadership in the global heterogeneous integration and 2.5D/3D IC packaging market.

Recent Development and Strategic Overview:

-

In November 2025, Intel introduced Foveros Direct 3D advanced packaging technology with sub‑10 µm hybrid bonding, enabling true vertical stacking of chiplets for AI and HPC workloads, delivering higher interconnect density and improved performance/power efficiency over legacy microbump approaches.

- In April 2025, ASE and Intel announced a strategic partnership to manufacture EMIB (Embedded Multi‑die Interconnect Bridge) packaging at ASE’s facilities, expanding advanced packaging capacity across Korea, Portugal and the U.S., boosting support for heterogeneous chiplet solutions.

Report Scope

|

Detail |

|

|

Market Size in 2025 |

USD 12.7 Bn |

|

Market Forecast Value in 2035 |

USD 38.4 Bn |

|

Growth Rate (CAGR) |

11.7% |

|

Forecast Period |

2026 – 2035 |

|

Historical Data Available for |

2021 – 2024 |

|

Market Size Units |

US$ Billion for Value |

|

Report Format |

Electronic (PDF) + Excel |

|

North America |

Europe |

Asia Pacific |

Middle East |

Africa |

South America |

|

|

|

|

|

|

|

Companies Covered |

|||||

|

|

|

|

|

|

Heterogeneous-Integration-and-2.5D/3D-IC-Packaging-Market Segmentation and Highlights

|

Segment |

Sub-segment |

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Technology Type |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Interconnect Technology |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Packaging Platform |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Chip Configuration |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Wafer Size |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Node Technology

|

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By Material Type |

|

|

Heterogeneous Integration and 2.5D/3D IC Packaging Market, By End-Use Industry |

|

Frequently Asked Questions

Table of Contents

- 1. Research Methodology and Assumptions

- 1.1. Definitions

- 1.2. Research Design and Approach

- 1.3. Data Collection Methods

- 1.4. Base Estimates and Calculations

- 1.5. Forecasting Models

- 1.5.1. Key Forecast Factors & Impact Analysis

- 1.6. Secondary Research

- 1.6.1. Open Sources

- 1.6.2. Paid Databases

- 1.6.3. Associations

- 1.7. Primary Research

- 1.7.1. Primary Sources

- 1.7.2. Primary Interviews with Stakeholders across Ecosystem

- 2. Executive Summary

- 2.1. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Outlook

- 2.1.1. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), and Forecasts, 2021-2035

- 2.1.2. Compounded Annual Growth Rate Analysis

- 2.1.3. Growth Opportunity Analysis

- 2.1.4. Segmental Share Analysis

- 2.1.5. Geographical Share Analysis

- 2.2. Market Analysis and Facts

- 2.3. Supply-Demand Analysis

- 2.4. Competitive Benchmarking

- 2.5. Go-to- Market Strategy

- 2.5.1. Customer/ End-use Industry Assessment

- 2.5.2. Growth Opportunity Data, 2026-2035

- 2.5.2.1. Regional Data

- 2.5.2.2. Country Data

- 2.5.2.3. Segmental Data

- 2.5.3. Identification of Potential Market Spaces

- 2.5.4. GAP Analysis

- 2.5.5. Potential Attractive Price Points

- 2.5.6. Prevailing Market Risks & Challenges

- 2.5.7. Preferred Sales & Marketing Strategies

- 2.5.8. Key Recommendations and Analysis

- 2.5.9. A Way Forward

- 2.1. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Outlook

- 3. Industry Data and Premium Insights

- 3.1. Global Semiconductors & Electronics Industry Overview, 2025

- 3.1.1. Semiconductors & Electronics Industry Ecosystem Analysis

- 3.1.2. Key Trends for Semiconductors & Electronics Industry

- 3.1.3. Regional Distribution for Semiconductors & Electronics Industry

- 3.2. Supplier Customer Data

- 3.3. Technology Roadmap and Developments

- 3.4. Trade Analysis

- 3.4.1. Import & Export Analysis, 2025

- 3.4.2. Top Importing Countries

- 3.4.3. Top Exporting Countries

- 3.5. Trump Tariff Impact Analysis

- 3.5.1. Manufacturer

- 3.5.1.1. Based on the component & Raw material

- 3.5.2. Supply Chain

- 3.5.3. End Consumer

- 3.5.1. Manufacturer

- 3.6. Raw Material Analysis

- 3.1. Global Semiconductors & Electronics Industry Overview, 2025

- 4. Market Overview

- 4.1. Market Dynamics

- 4.1.1. Drivers

- Growing demand for high4.1.1.1. ‑performance computing, AI, 5G, and IoT applications

- Miniaturization and demand for compact, energy4.1.1.2. ‑efficient electronic devices

- 4.1.1.3. Advancements in heterogeneous integration technologies (e.g., TSVs, interposers, chiplets) enhancing performance and design flexibility

- 4.1.2. Restraints

- 4.1.2.1. High manufacturing and design complexity costs

- 4.1.2.2. Thermal management and reliability challenges due to dense stacking

- 4.1.1. Drivers

- 4.2. Key Trend Analysis

- 4.3. Regulatory Framework

- 4.3.1. Key Regulations, Norms, and Subsidies, by Key Countries

- 4.3.2. Tariffs and Standards

- 4.3.3. Impact Analysis of Regulations on the Market

- 4.4. Value Chain Analysis

- 4.4.1. Raw Materials & Substrates

- 4.4.2. Wafer Fabrication & Dicing

- 4.4.3. Distribution & Assembly Services

- 4.4.4. End‑User Applications

- 4.5. Porter’s Five Forces Analysis

- 4.6. PESTEL Analysis

- 4.7. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Demand

- 4.7.1. Historical Market Size – Value (US$ Bn), 2020-2024

- 4.7.2. Current and Future Market Size – Value (US$ Bn), 2026–2035

- 4.7.2.1. Y-o-Y Growth Trends

- 4.7.2.2. Absolute $ Opportunity Assessment

- 4.1. Market Dynamics

- 5. Competition Landscape

- 5.1. Competition structure

- 5.1.1. Fragmented v/s consolidated

- 5.2. Company Share Analysis, 2025

- 5.2.1. Global Company Market Share

- 5.2.2. By Region

- 5.2.2.1. North America

- 5.2.2.2. Europe

- 5.2.2.3. Asia Pacific

- 5.2.2.4. Middle East

- 5.2.2.5. Africa

- 5.2.2.6. South America

- 5.3. Product Comparison Matrix

- 5.3.1. Specifications

- 5.3.2. Market Positioning

- 5.3.3. Pricing

- 5.1. Competition structure

- 6. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Technology Type

- 6.1. Key Segment Analysis

- 6.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Technology Type, 2021-2035

- 6.2.1. 5D IC Packaging

- 6.2.1.1. Interposer-based

- 6.2.1.2. Fan-out Wafer Level Packaging (FOWLP)

- 6.2.2. 3D IC Packaging

- 6.2.2.1. Through-Silicon Via (TSV)

- 6.2.2.2. Monolithic 3D

- 6.2.2.3. Wafer-on-Wafer (WoW)

- 6.2.2.4. Die-on-Wafer (DoW)

- 6.2.2.5. Die-on-Die (DoD)

- 6.2.3. Chiplet-based Integration

- 6.2.4. Hybrid Bonding

- 6.2.1. 5D IC Packaging

- 7. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Interconnect Technology

- 7.1. Key Segment Analysis

- 7.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Interconnect Technology, 2021-2035

- 7.2.1. Micro-bump Interconnects

- 7.2.2. Copper Pillar Interconnects

- 7.2.3. Through-Silicon Via (TSV) Interconnects

- 7.2.4. Hybrid Bonding Interconnects

- 7.2.5. Wire Bonding

- 7.2.6. Redistribution Layer (RDL)

- 8. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Packaging Platform

- 8.1. Key Segment Analysis

- 8.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Packaging Platform, 2021-2035

- 8.2.1. Silicon Interposer

- 8.2.2. Organic Interposer

- 8.2.3. Glass Interposer

- 8.2.4. Fan-Out Package-on-Package (FO-PoP)

- 8.2.5. Embedded Multi-die Interconnect Bridge (EMIB)

- 8.2.6. Chip-on-Wafer-on-Substrate (CoWoS)

- 8.2.7. Integrated Fan-Out (InFO)

- 9. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Chip Configuration

- 9.1. Key Segment Analysis

- 9.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Chip Configuration, 2021-2035

- 9.2.1. Homogeneous Integration

- 9.2.2. Heterogeneous Integration

- 9.2.3. Logic + Memory

- 9.2.3.1. Logic + RF

- 9.2.3.2. Logic + Sensor

- 9.2.3.3. Logic + Power

- 9.2.3.4. Multi-function Integration

- 10. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Wafer Size

- 10.1. Key Segment Analysis

- 10.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Wafer Size, 2021-2035

- 10.2.1. 100mm

- 10.2.2. 150mm

- 10.2.3. 200mm

- 10.2.4. 300mm

- 10.2.5. 450mm (Emerging)

- 11. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Node Technology

- 11.1. Key Segment Analysis

- 11.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Node Technology, 2021-2035

- 11.2.1. Above 10nm

- 11.2.2. 7nm-10nm

- 11.2.3. 5nm-7nm

- 11.2.4. 3nm-5nm

- 11.2.5. Below 3nm

- 12. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by Material Type

- 12.1. Key Segment Analysis

- 12.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Material Type, 2021-2035

- 12.2.1. Silicon-based

- 12.2.2. Organic Materials

- 12.2.3. Glass Substrates

- 12.2.4. Ceramic Materials

- 12.2.5. Composite Materials

- 13. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis, by End-Use Industry

- 13.1. Key Segment Analysis

- 13.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by End-Use Industry, 2021-2035

- 13.2.1. Consumer Electronics

- 13.2.2. Data Centers & Cloud Computing

- 13.2.3. Automotive & Transportation

- 13.2.4. Telecommunications & Networking

- 13.2.5. Artificial Intelligence & Machine Learning

- 13.2.6. Industrial & Manufacturing

- 13.2.7. Healthcare & Medical Devices

- 13.2.8. Aerospace & Defense

- 13.2.9. Financial Services & FinTech

- 13.2.10. Others

- 14. Global Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis and Forecasts, by Region

- 14.1. Key Findings

- 14.2. Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, by Region, 2021-2035

- 14.2.1. North America

- 14.2.2. Europe

- 14.2.3. Asia Pacific

- 14.2.4. Middle East

- 14.2.5. Africa

- 14.2.6. South America

- 15. North America Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 15.1. Key Segment Analysis

- 15.2. Regional Snapshot

- 15.3. North America Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 15.3.1. Technology Type

- 15.3.2. Interconnect Technology

- 15.3.3. Packaging Platform

- 15.3.4. Chip Configuration

- 15.3.5. Wafer Size

- 15.3.6. Node Technology

- 15.3.7. Material Type

- 15.3.8. End-Use Industry

- 15.3.9. Country

- 15.3.9.1. USA

- 15.3.9.2. Canada

- 15.3.9.3. Mexico

- 15.4. USA Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 15.4.1. Country Segmental Analysis

- 15.4.2. Technology Type

- 15.4.3. Interconnect Technology

- 15.4.4. Packaging Platform

- 15.4.5. Chip Configuration

- 15.4.6. Wafer Size

- 15.4.7. Node Technology

- 15.4.8. Material Type

- 15.4.9. End-Use Industry

- 15.5. Canada Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 15.5.1. Country Segmental Analysis

- 15.5.2. Technology Type

- 15.5.3. Interconnect Technology

- 15.5.4. Packaging Platform

- 15.5.5. Chip Configuration

- 15.5.6. Wafer Size

- 15.5.7. Node Technology

- 15.5.8. Material Type

- 15.5.9. End-Use Industry

- 15.6. Mexico Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 15.6.1. Country Segmental Analysis

- 15.6.2. Technology Type

- 15.6.3. Interconnect Technology

- 15.6.4. Packaging Platform

- 15.6.5. Chip Configuration

- 15.6.6. Wafer Size

- 15.6.7. Node Technology

- 15.6.8. Material Type

- 15.6.9. End-Use Industry

- 16. Europe Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 16.1. Key Segment Analysis

- 16.2. Regional Snapshot

- 16.3. Europe Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 16.3.1. Technology Type

- 16.3.2. Interconnect Technology

- 16.3.3. Packaging Platform

- 16.3.4. Chip Configuration

- 16.3.5. Wafer Size

- 16.3.6. Node Technology

- 16.3.7. Material Type

- 16.3.8. End-Use Industry

- 16.3.9. Country

- 16.3.9.1. Germany

- 16.3.9.2. United Kingdom

- 16.3.9.3. France

- 16.3.9.4. Italy

- 16.3.9.5. Spain

- 16.3.9.6. Netherlands

- 16.3.9.7. Nordic Countries

- 16.3.9.8. Poland

- 16.3.9.9. Russia & CIS

- 16.3.9.10. Rest of Europe

- 16.4. Germany Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.4.1. Country Segmental Analysis

- 16.4.2. Technology Type

- 16.4.3. Interconnect Technology

- 16.4.4. Packaging Platform

- 16.4.5. Chip Configuration

- 16.4.6. Wafer Size

- 16.4.7. Node Technology

- 16.4.8. Material Type

- 16.4.9. End-Use Industry

- 16.5. United Kingdom Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.5.1. Country Segmental Analysis

- 16.5.2. Technology Type

- 16.5.3. Interconnect Technology

- 16.5.4. Packaging Platform

- 16.5.5. Chip Configuration

- 16.5.6. Wafer Size

- 16.5.7. Node Technology

- 16.5.8. Material Type

- 16.5.9. End-Use Industry

- 16.6. France Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.6.1. Country Segmental Analysis

- 16.6.2. Technology Type

- 16.6.3. Interconnect Technology

- 16.6.4. Packaging Platform

- 16.6.5. Chip Configuration

- 16.6.6. Wafer Size

- 16.6.7. Node Technology

- 16.6.8. Material Type

- 16.6.9. End-Use Industry

- 16.7. Italy Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.7.1. Country Segmental Analysis

- 16.7.2. Technology Type

- 16.7.3. Interconnect Technology

- 16.7.4. Packaging Platform

- 16.7.5. Chip Configuration

- 16.7.6. Wafer Size

- 16.7.7. Node Technology

- 16.7.8. Material Type

- 16.7.9. End-Use Industry

- 16.8. Spain Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.8.1. Country Segmental Analysis

- 16.8.2. Technology Type

- 16.8.3. Interconnect Technology

- 16.8.4. Packaging Platform

- 16.8.5. Chip Configuration

- 16.8.6. Wafer Size

- 16.8.7. Node Technology

- 16.8.8. Material Type

- 16.8.9. End-Use Industry

- 16.9. Netherlands Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.9.1. Country Segmental Analysis

- 16.9.2. Technology Type

- 16.9.3. Interconnect Technology

- 16.9.4. Packaging Platform

- 16.9.5. Chip Configuration

- 16.9.6. Wafer Size

- 16.9.7. Node Technology

- 16.9.8. Material Type

- 16.9.9. End-Use Industry

- 16.10. Nordic Countries Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.10.1. Country Segmental Analysis

- 16.10.2. Technology Type

- 16.10.3. Interconnect Technology

- 16.10.4. Packaging Platform

- 16.10.5. Chip Configuration

- 16.10.6. Wafer Size

- 16.10.7. Node Technology

- 16.10.8. Material Type

- 16.10.9. End-Use Industry

- 16.11. Poland Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.11.1. Country Segmental Analysis

- 16.11.2. Technology Type

- 16.11.3. Interconnect Technology

- 16.11.4. Packaging Platform

- 16.11.5. Chip Configuration

- 16.11.6. Wafer Size

- 16.11.7. Node Technology

- 16.11.8. Material Type

- 16.11.9. End-Use Industry

- 16.12. Russia & CIS Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.12.1. Country Segmental Analysis

- 16.12.2. Technology Type

- 16.12.3. Interconnect Technology

- 16.12.4. Packaging Platform

- 16.12.5. Chip Configuration

- 16.12.6. Wafer Size

- 16.12.7. Node Technology

- 16.12.8. Material Type

- 16.12.9. End-Use Industry

- 16.13. Rest of Europe Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 16.13.1. Country Segmental Analysis

- 16.13.2. Technology Type

- 16.13.3. Interconnect Technology

- 16.13.4. Packaging Platform

- 16.13.5. Chip Configuration

- 16.13.6. Wafer Size

- 16.13.7. Node Technology

- 16.13.8. Material Type

- 16.13.9. End-Use Industry

- 17. Asia Pacific Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 17.1. Key Segment Analysis

- 17.2. Regional Snapshot

- 17.3. Asia Pacific Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 17.3.1. Technology Type

- 17.3.2. Interconnect Technology

- 17.3.3. Packaging Platform

- 17.3.4. Chip Configuration

- 17.3.5. Wafer Size

- 17.3.6. Node Technology

- 17.3.7. Material Type

- 17.3.8. End-Use Industry

- 17.3.9. Country

- 17.3.9.1. China

- 17.3.9.2. India

- 17.3.9.3. Japan

- 17.3.9.4. South Korea

- 17.3.9.5. Australia and New Zealand

- 17.3.9.6. Indonesia

- 17.3.9.7. Malaysia

- 17.3.9.8. Thailand

- 17.3.9.9. Vietnam

- 17.3.9.10. Rest of Asia Pacific

- 17.4. China Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.4.1. Country Segmental Analysis

- 17.4.2. Technology Type

- 17.4.3. Interconnect Technology

- 17.4.4. Packaging Platform

- 17.4.5. Chip Configuration

- 17.4.6. Wafer Size

- 17.4.7. Node Technology

- 17.4.8. Material Type

- 17.4.9. End-Use Industry

- 17.5. India Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.5.1. Country Segmental Analysis

- 17.5.2. Technology Type

- 17.5.3. Interconnect Technology

- 17.5.4. Packaging Platform

- 17.5.5. Chip Configuration

- 17.5.6. Wafer Size

- 17.5.7. Node Technology

- 17.5.8. Material Type

- 17.5.9. End-Use Industry

- 17.6. Japan Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.6.1. Country Segmental Analysis

- 17.6.2. Technology Type

- 17.6.3. Interconnect Technology

- 17.6.4. Packaging Platform

- 17.6.5. Chip Configuration

- 17.6.6. Wafer Size

- 17.6.7. Node Technology

- 17.6.8. Material Type

- 17.6.9. End-Use Industry

- 17.7. South Korea Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.7.1. Country Segmental Analysis

- 17.7.2. Technology Type

- 17.7.3. Interconnect Technology

- 17.7.4. Packaging Platform

- 17.7.5. Chip Configuration

- 17.7.6. Wafer Size

- 17.7.7. Node Technology

- 17.7.8. Material Type

- 17.7.9. End-Use Industry

- 17.8. Australia and New Zealand Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.8.1. Country Segmental Analysis

- 17.8.2. Technology Type

- 17.8.3. Interconnect Technology

- 17.8.4. Packaging Platform

- 17.8.5. Chip Configuration

- 17.8.6. Wafer Size

- 17.8.7. Node Technology

- 17.8.8. Material Type

- 17.8.9. End-Use Industry

- 17.9. Indonesia Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.9.1. Country Segmental Analysis

- 17.9.2. Technology Type

- 17.9.3. Interconnect Technology

- 17.9.4. Packaging Platform

- 17.9.5. Chip Configuration

- 17.9.6. Wafer Size

- 17.9.7. Node Technology

- 17.9.8. Material Type

- 17.9.9. End-Use Industry

- 17.10. Malaysia Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.10.1. Country Segmental Analysis

- 17.10.2. Technology Type

- 17.10.3. Interconnect Technology

- 17.10.4. Packaging Platform

- 17.10.5. Chip Configuration

- 17.10.6. Wafer Size

- 17.10.7. Node Technology

- 17.10.8. Material Type

- 17.10.9. End-Use Industry

- 17.11. Thailand Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.11.1. Country Segmental Analysis

- 17.11.2. Technology Type

- 17.11.3. Interconnect Technology

- 17.11.4. Packaging Platform

- 17.11.5. Chip Configuration

- 17.11.6. Wafer Size

- 17.11.7. Node Technology

- 17.11.8. Material Type

- 17.11.9. End-Use Industry

- 17.12. Vietnam Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.12.1. Country Segmental Analysis

- 17.12.2. Technology Type

- 17.12.3. Interconnect Technology

- 17.12.4. Packaging Platform

- 17.12.5. Chip Configuration

- 17.12.6. Wafer Size

- 17.12.7. Node Technology

- 17.12.8. Material Type

- 17.12.9. End-Use Industry

- 17.13. Rest of Asia Pacific Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 17.13.1. Country Segmental Analysis

- 17.13.2. Technology Type

- 17.13.3. Interconnect Technology

- 17.13.4. Packaging Platform

- 17.13.5. Chip Configuration

- 17.13.6. Wafer Size

- 17.13.7. Node Technology

- 17.13.8. Material Type

- 17.13.9. End-Use Industry

- 18. Middle East Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 18.1. Key Segment Analysis

- 18.2. Regional Snapshot

- 18.3. Middle East Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 18.3.1. Technology Type

- 18.3.2. Interconnect Technology

- 18.3.3. Packaging Platform

- 18.3.4. Chip Configuration

- 18.3.5. Wafer Size

- 18.3.6. Node Technology

- 18.3.7. Material Type

- 18.3.8. End-Use Industry

- 18.3.9. Country

- 18.3.9.1. Turkey

- 18.3.9.2. UAE

- 18.3.9.3. Saudi Arabia

- 18.3.9.4. Israel

- 18.3.9.5. Rest of Middle East

- 18.4. Turkey Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 18.4.1. Country Segmental Analysis

- 18.4.2. Technology Type

- 18.4.3. Interconnect Technology

- 18.4.4. Packaging Platform

- 18.4.5. Chip Configuration

- 18.4.6. Wafer Size

- 18.4.7. Node Technology

- 18.4.8. Material Type

- 18.4.9. End-Use Industry

- 18.5. UAE Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 18.5.1. Country Segmental Analysis

- 18.5.2. Technology Type

- 18.5.3. Interconnect Technology

- 18.5.4. Packaging Platform

- 18.5.5. Chip Configuration

- 18.5.6. Wafer Size

- 18.5.7. Node Technology

- 18.5.8. Material Type

- 18.5.9. End-Use Industry

- 18.6. Saudi Arabia Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 18.6.1. Country Segmental Analysis

- 18.6.2. Technology Type

- 18.6.3. Interconnect Technology

- 18.6.4. Packaging Platform

- 18.6.5. Chip Configuration

- 18.6.6. Wafer Size

- 18.6.7. Node Technology

- 18.6.8. Material Type

- 18.6.9. End-Use Industry

- 18.7. Israel Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 18.7.1. Country Segmental Analysis

- 18.7.2. Technology Type

- 18.7.3. Interconnect Technology

- 18.7.4. Packaging Platform

- 18.7.5. Chip Configuration

- 18.7.6. Wafer Size

- 18.7.7. Node Technology

- 18.7.8. Material Type

- 18.7.9. End-Use Industry

- 18.8. Rest of Middle East Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 18.8.1. Country Segmental Analysis

- 18.8.2. Technology Type

- 18.8.3. Interconnect Technology

- 18.8.4. Packaging Platform

- 18.8.5. Chip Configuration

- 18.8.6. Wafer Size

- 18.8.7. Node Technology

- 18.8.8. Material Type

- 18.8.9. End-Use Industry

- 19. Africa Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 19.1. Key Segment Analysis

- 19.2. Regional Snapshot

- 19.3. Africa Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 19.3.1. Technology Type

- 19.3.2. Interconnect Technology

- 19.3.3. Packaging Platform

- 19.3.4. Chip Configuration

- 19.3.5. Wafer Size

- 19.3.6. Node Technology

- 19.3.7. Material Type

- 19.3.8. End-Use Industry

- 19.3.9. Country

- 19.3.9.1. South Africa

- 19.3.9.2. Egypt

- 19.3.9.3. Nigeria

- 19.3.9.4. Algeria

- 19.3.9.5. Rest of Africa

- 19.4. South Africa Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 19.4.1. Country Segmental Analysis

- 19.4.2. Technology Type

- 19.4.3. Interconnect Technology

- 19.4.4. Packaging Platform

- 19.4.5. Chip Configuration

- 19.4.6. Wafer Size

- 19.4.7. Node Technology

- 19.4.8. Material Type

- 19.4.9. End-Use Industry

- 19.5. Egypt Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 19.5.1. Country Segmental Analysis

- 19.5.2. Technology Type

- 19.5.3. Interconnect Technology

- 19.5.4. Packaging Platform

- 19.5.5. Chip Configuration

- 19.5.6. Wafer Size

- 19.5.7. Node Technology

- 19.5.8. Material Type

- 19.5.9. End-Use Industry

- 19.6. Nigeria Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 19.6.1. Country Segmental Analysis

- 19.6.2. Technology Type

- 19.6.3. Interconnect Technology

- 19.6.4. Packaging Platform

- 19.6.5. Chip Configuration

- 19.6.6. Wafer Size

- 19.6.7. Node Technology

- 19.6.8. Material Type

- 19.6.9. End-Use Industry

- 19.7. Algeria Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 19.7.1. Country Segmental Analysis

- 19.7.2. Technology Type

- 19.7.3. Interconnect Technology

- 19.7.4. Packaging Platform

- 19.7.5. Chip Configuration

- 19.7.6. Wafer Size

- 19.7.7. Node Technology

- 19.7.8. Material Type

- 19.7.9. End-Use Industry

- 19.8. Rest of Africa Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 19.8.1. Country Segmental Analysis

- 19.8.2. Technology Type

- 19.8.3. Interconnect Technology

- 19.8.4. Packaging Platform

- 19.8.5. Chip Configuration

- 19.8.6. Wafer Size

- 19.8.7. Node Technology

- 19.8.8. Material Type

- 19.8.9. End-Use Industry

- 20. South America Heterogeneous Integration and 2.5D/3D IC Packaging Market Analysis

- 20.1. Key Segment Analysis

- 20.2. Regional Snapshot

- 20.3. South America Heterogeneous Integration and 2.5D/3D IC Packaging Market Size (Value - US$ Bn), Analysis, and Forecasts, 2021-2035

- 20.3.1. Technology Type

- 20.3.2. Interconnect Technology

- 20.3.3. Packaging Platform

- 20.3.4. Chip Configuration

- 20.3.5. Wafer Size

- 20.3.6. Node Technology

- 20.3.7. Material Type

- 20.3.8. End-Use Industry

- 20.3.9. Country

- 20.3.9.1. Brazil

- 20.3.9.2. Argentina

- 20.3.9.3. Rest of South America

- 20.4. Brazil Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 20.4.1. Country Segmental Analysis

- 20.4.2. Technology Type

- 20.4.3. Interconnect Technology

- 20.4.4. Packaging Platform

- 20.4.5. Chip Configuration

- 20.4.6. Wafer Size

- 20.4.7. Node Technology

- 20.4.8. Material Type

- 20.4.9. End-Use Industry

- 20.5. Argentina Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 20.5.1. Country Segmental Analysis

- 20.5.2. Technology Type

- 20.5.3. Interconnect Technology

- 20.5.4. Packaging Platform

- 20.5.5. Chip Configuration

- 20.5.6. Wafer Size

- 20.5.7. Node Technology

- 20.5.8. Material Type

- 20.5.9. End-Use Industry

- 20.6. Rest of South America Heterogeneous Integration and 2.5D/3D IC Packaging Market

- 20.6.1. Country Segmental Analysis

- 20.6.2. Technology Type

- 20.6.3. Interconnect Technology

- 20.6.4. Packaging Platform

- 20.6.5. Chip Configuration

- 20.6.6. Wafer Size

- 20.6.7. Node Technology

- 20.6.8. Material Type

- 20.6.9. End-Use Industry

- 21. Key Players/ Company Profile

- 21.1. Advanced Micro Devices (AMD)

- 21.1.1. Company Details/ Overview

- 21.1.2. Company Financials

- 21.1.3. Key Customers and Competitors

- 21.1.4. Business/ Industry Portfolio

- 21.1.5. Product Portfolio/ Specification Details

- 21.1.6. Pricing Data

- 21.1.7. Strategic Overview

- 21.1.8. Recent Developments

- 21.2. Amkor Technology

- 21.3. ASE Technology Holding Co., Ltd.

- 21.4. GlobalFoundries

- 21.5. Indium Corporation

- 21.6. Intel Corporation

- 21.7. JCET Group

- 21.8. Marvell Technology Group

- 21.9. Micross Components, Inc.

- 21.10. NHanced Semiconductors, Inc.

- 21.11. NVIDIA Corporation

- 21.12. Powertech Technology Inc. (PTI)

- 21.13. Samsung Electronics Co., Ltd.

- 21.14. Siliconware Precision Industries Co., Ltd. (SPIL)

- 21.15. SK Hynix Inc.

- 21.16. Taiwan Semiconductor Manufacturing Company (TSMC)

- 21.17. United Microelectronics Corporation (UMC)

- 21.18. Other Key Players

- 21.1. Advanced Micro Devices (AMD)

Note* - This is just tentative list of players. While providing the report, we will cover more number of players based on their revenue and share for each geography

Research Design

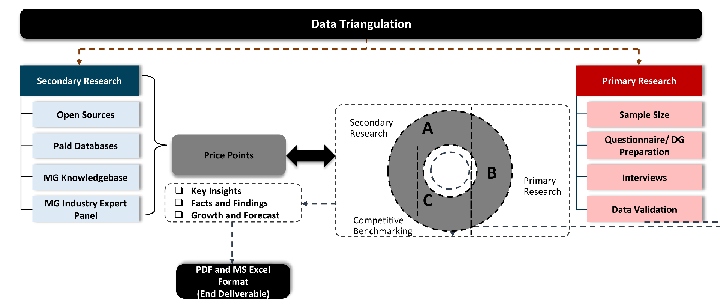

Our research design integrates both demand-side and supply-side analysis through a balanced combination of primary and secondary research methodologies. By utilizing both bottom-up and top-down approaches alongside rigorous data triangulation methods, we deliver robust market intelligence that supports strategic decision-making.

MarketGenics' comprehensive research design framework ensures the delivery of accurate, reliable, and actionable market intelligence. Through the integration of multiple research approaches, rigorous validation processes, and expert analysis, we provide our clients with the insights needed to make informed strategic decisions and capitalize on market opportunities.

MarketGenics leverages a dedicated industry panel of experts and a comprehensive suite of paid databases to effectively collect, consolidate, and analyze market intelligence.

Our approach has consistently proven to be reliable and effective in generating accurate market insights, identifying key industry trends, and uncovering emerging business opportunities.

Through both primary and secondary research, we capture and analyze critical company-level data such as manufacturing footprints, including technical centers, R&D facilities, sales offices, and headquarters.

Our expert panel further enhances our ability to estimate market size for specific brands based on validated field-level intelligence.

Our data mining techniques incorporate both parametric and non-parametric methods, allowing for structured data collection, sorting, processing, and cleaning.

Demand projections are derived from large-scale data sets analyzed through proprietary algorithms, culminating in robust and reliable market sizing.

Research Approach

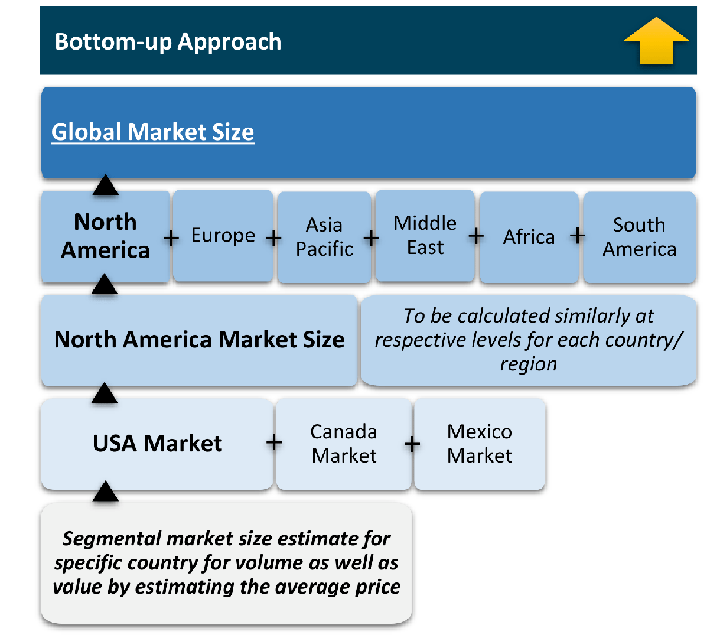

The bottom-up approach builds market estimates by starting with the smallest addressable market units and systematically aggregating them to create comprehensive market size projections.

This method begins with specific, granular data points and builds upward to create the complete market landscape.

Customer Analysis → Segmental Analysis → Geographical Analysis

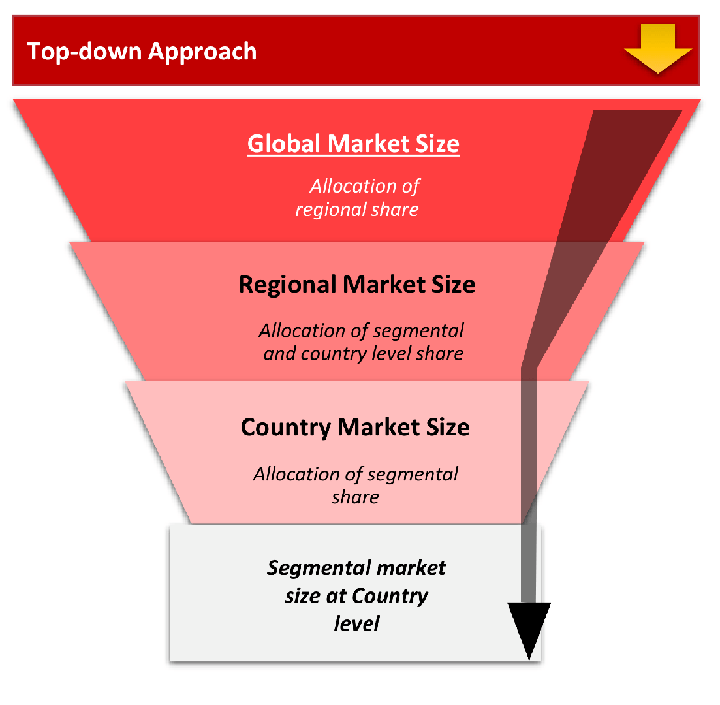

The top-down approach starts with the broadest possible market data and systematically narrows it down through a series of filters and assumptions to arrive at specific market segments or opportunities.

This method begins with the big picture and works downward to increasingly specific market slices.

TAM → SAM → SOM

Research Methods

Desk / Secondary Research

While analysing the market, we extensively study secondary sources, directories, and databases to identify and collect information useful for this technical, market-oriented, and commercial report. Secondary sources that we utilize are not only the public sources, but it is a combination of Open Source, Associations, Paid Databases, MG Repository & Knowledgebase, and others.

- Company websites, annual reports, financial reports, broker reports, and investor presentations

- National government documents, statistical databases and reports

- News articles, press releases and web-casts specific to the companies operating in the market, Magazines, reports, and others

- We gather information from commercial data sources for deriving company specific data such as segmental revenue, share for geography, product revenue, and others

- Internal and external proprietary databases (industry-specific), relevant patent, and regulatory databases

- Governing Bodies, Government Organizations

- Relevant Authorities, Country-specific Associations for Industries

We also employ the model mapping approach to estimate the product level market data through the players' product portfolio

Primary Research

Primary research/ interviews is vital in analyzing the market. Most of the cases involves paid primary interviews. Primary sources include primary interviews through e-mail interactions, telephonic interviews, surveys as well as face-to-face interviews with the different stakeholders across the value chain including several industry experts.

| Type of Respondents | Number of Primaries |

|---|---|

| Tier 2/3 Suppliers | ~20 |

| Tier 1 Suppliers | ~25 |

| End-users | ~25 |

| Industry Expert/ Panel/ Consultant | ~30 |

| Total | ~100 |

MG Knowledgebase

• Repository of industry blog, newsletter and case studies

• Online platform covering detailed market reports, and company profiles

Forecasting Factors and Models

Forecasting Factors

- Historical Trends – Past market patterns, cycles, and major events that shaped how markets behave over time. Understanding past trends helps predict future behavior.

- Industry Factors – Specific characteristics of the industry like structure, regulations, and innovation cycles that affect market dynamics.

- Macroeconomic Factors – Economic conditions like GDP growth, inflation, and employment rates that affect how much money people have to spend.

- Demographic Factors – Population characteristics like age, income, and location that determine who can buy your product.

- Technology Factors – How quickly people adopt new technology and how much technology infrastructure exists.

- Regulatory Factors – Government rules, laws, and policies that can help or restrict market growth.

- Competitive Factors – Analyzing competition structure such as degree of competition and bargaining power of buyers and suppliers.

Forecasting Models / Techniques

Multiple Regression Analysis

- Identify and quantify factors that drive market changes

- Statistical modeling to establish relationships between market drivers and outcomes

Time Series Analysis – Seasonal Patterns

- Understand regular cyclical patterns in market demand

- Advanced statistical techniques to separate trend, seasonal, and irregular components

Time Series Analysis – Trend Analysis

- Identify underlying market growth patterns and momentum

- Statistical analysis of historical data to project future trends

Expert Opinion – Expert Interviews

- Gather deep industry insights and contextual understanding

- In-depth interviews with key industry stakeholders

Multi-Scenario Development

- Prepare for uncertainty by modeling different possible futures

- Creating optimistic, pessimistic, and most likely scenarios

Time Series Analysis – Moving Averages

- Sophisticated forecasting for complex time series data

- Auto-regressive integrated moving average models with seasonal components

Econometric Models

- Apply economic theory to market forecasting

- Sophisticated economic models that account for market interactions

Expert Opinion – Delphi Method

- Harness collective wisdom of industry experts

- Structured, multi-round expert consultation process

Monte Carlo Simulation

- Quantify uncertainty and probability distributions

- Thousands of simulations with varying input parameters

Research Analysis

Our research framework is built upon the fundamental principle of validating market intelligence from both demand and supply perspectives. This dual-sided approach ensures comprehensive market understanding and reduces the risk of single-source bias.

Demand-Side Analysis: We understand end-user/application behavior, preferences, and market needs along with the penetration of the product for specific application.

Supply-Side Analysis: We estimate overall market revenue, analyze the segmental share along with industry capacity, competitive landscape, and market structure.

Validation & Evaluation

Data triangulation is a validation technique that uses multiple methods, sources, or perspectives to examine the same research question, thereby increasing the credibility and reliability of research findings. In market research, triangulation serves as a quality assurance mechanism that helps identify and minimize bias, validate assumptions, and ensure accuracy in market estimates.

- Data Source Triangulation – Using multiple data sources to examine the same phenomenon

- Methodological Triangulation – Using multiple research methods to study the same research question

- Investigator Triangulation – Using multiple researchers or analysts to examine the same data

- Theoretical Triangulation – Using multiple theoretical perspectives to interpret the same data

Custom Market Research Services

We will customise the research for you, in case the report listed above does not meet your requirements.

Get 10% Free Customisation